# A method for designing high-frequency operational amplifiers using the $g_m/I_d$ methodology

Alexandre QUENON, Fortunato DUALIBE, Papy NDUNGIDI KIAZAYILA

Operational amplifiers are one of the most used devices in analog electronics. Even accounting with a vast know-how on analog design, the design of such circuits is time-consuming. The main idea behind this project consists in developing a design methodology that allows to save time at the design phase. As a proof of concept we have chosen an HF application, which are well-known because of the difficulty to achieve the target specifications by means of traditional design. We first chose the op amp topology and then built its high-frequency model. To design our amplifier we used the so-called "g<sub>m</sub>/l<sub>d</sub> methodology"<sup>[1]</sup>, which is based on the universal transconductance-to-current ratio of the MOS transistor. Finally, we simulated the circuit with CADENCE SPECTRE.

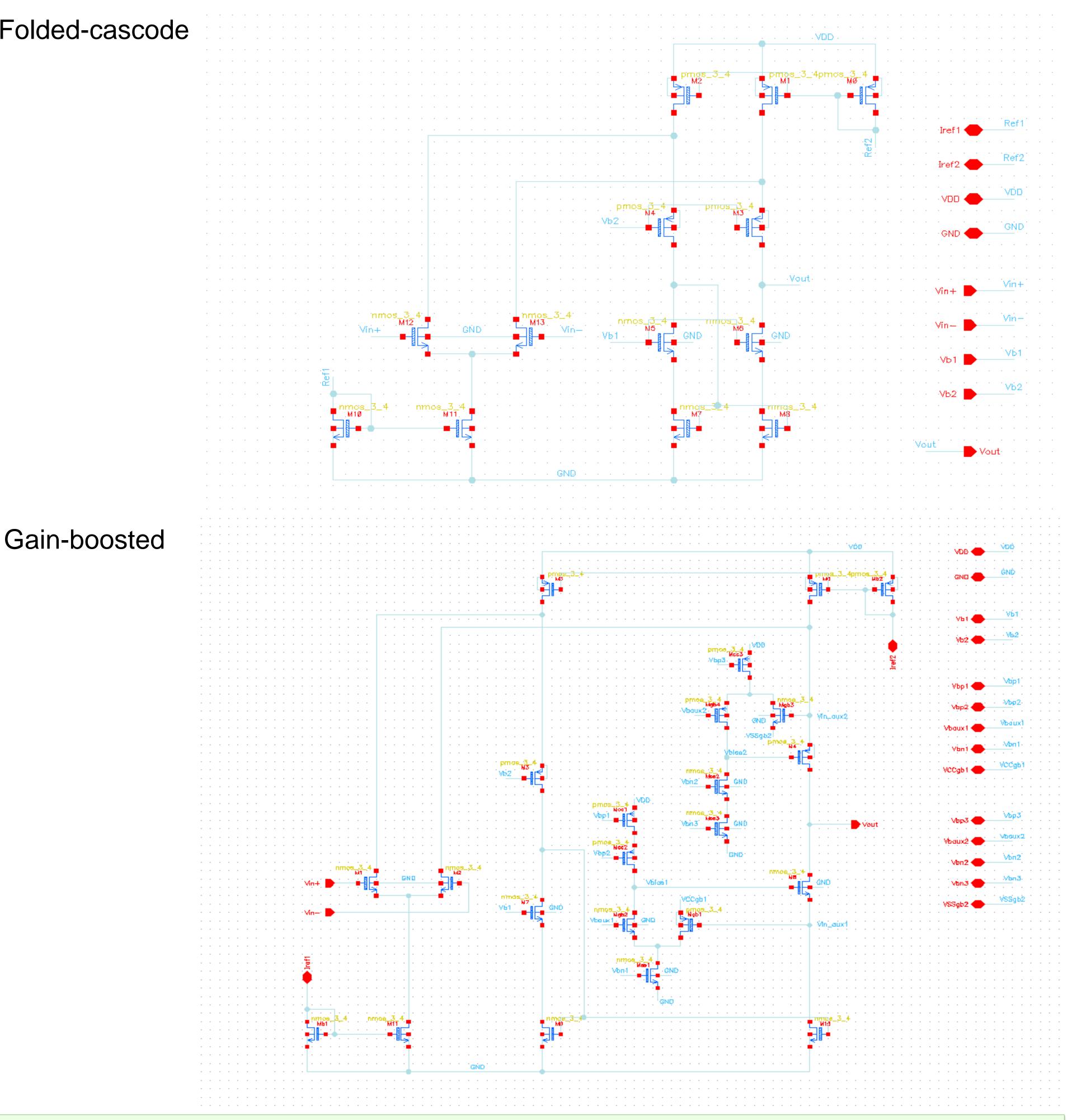

Folded-cascode

### 4. Circuits schematics

### 1. Specifications

Four main specifications:

- 1.  $f_T = unity$ -gain frequency > 500 MHz (target = 1 GHz);

- 2. Ao = open-loop DC gain > 60 dB

- $PM = phase margin > 45^{\circ} (target = 60^{\circ});$ 3.

- 4. CL = load capacitance = 1-2 pF.

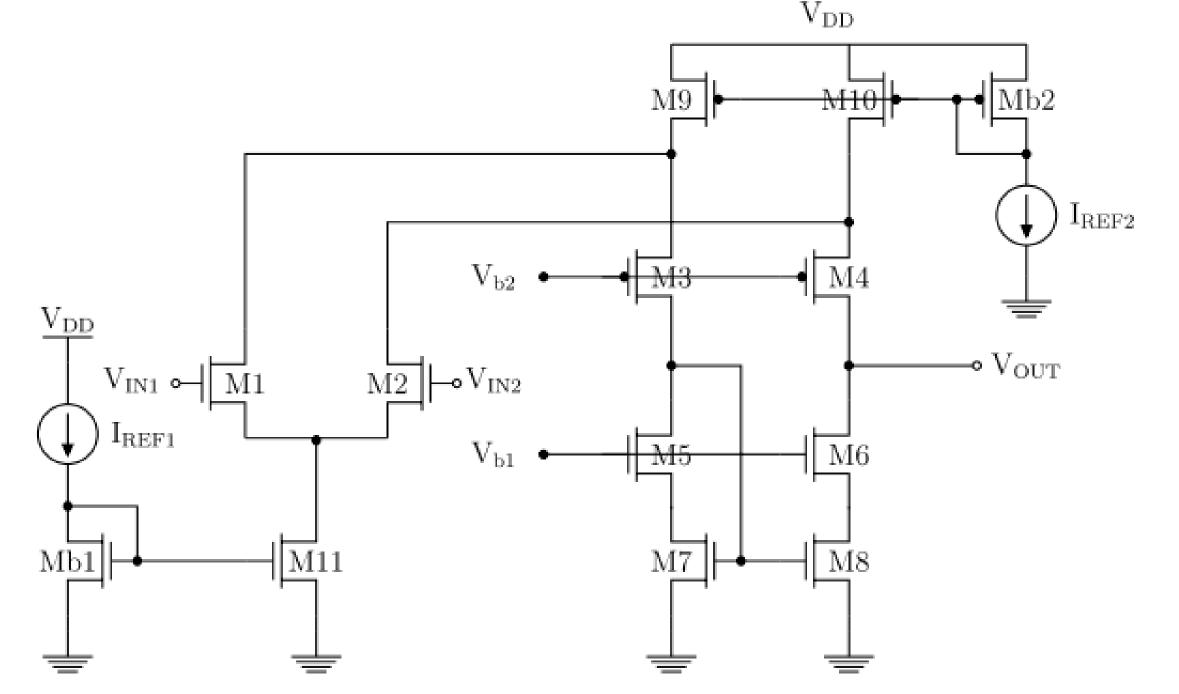

2. Topology

#### Folded-cascode / gain-boosted op amp:

On the one hand, we need a high-speed operational amplifier. So we have to use minimum transistor's size in order to decrease junctions capacitances. But this implies higher drain-to-source voltages and thus lower signal swing. This leads to choose a folded-cascode architecture <sup>[2]</sup>. On the other hand, we need a high-gain amplifier. In this case, the gain-boosted cascode topology is more appropriate. We have studied both topologies and chosen the best trade-off.

#### Single-ended VS fully-differential:

- **fully-differential** = best performances in terms on bulk noise and power supply rejection. Need of an extra CMRR circuit to set the outputs DC level of the op amp.

- **single-ended** = easier to design but more prone to noise and power supply variations effects.

Single-ended folded-cascode structure:

### 5. Results

#### Voltage supply = 1.8 V. Technology = Lfoundry 150nm.

| Amplifier       | DC gain [dB] | Unity-gain freq [Hz] | Phase margin [°] |

|-----------------|--------------|----------------------|------------------|

| Folded-cascode: | 38.4         | 877.8 M              | 48.02            |

| Gain-boosted:   | 62           | 937.2 M              | 41.77            |

#### How to achieve better results?

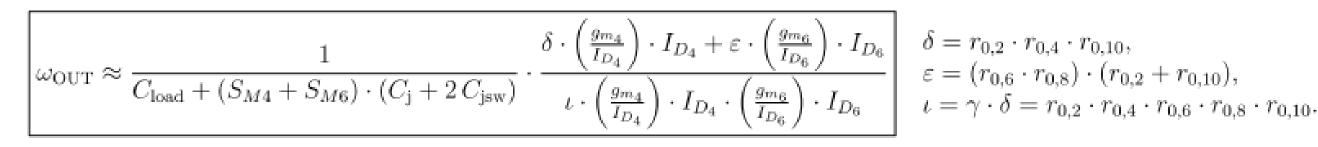

## 3. $g_m/I_d$ methodology

#### Steps:

- 1. High-frequency model (more or less accurate).

- Poles and zeros, DC gain, Impedances: parametrical 2. characterization by means of the  $g_m/I_d$  of the involved transistors.

- 3. Parameters computation (PM,  $f_{T}$ ...).

- 4. SPECTRE simulations using the BSIM4 model.

#### Example:

- Using more accurate models (EKV or ACM models) at the hand calculations steps.

- Running optimization procedures in closed-loop that make use of classic optimization algorithms.

### Conclusion

In this work we used the  $g_m/I_d$  methodology to design an amplifier targeting high frequency applications. We proposed a design method, which consists in choosing the amplifier topology according to the specifications and then building its high-frequency model. Based on this model, one can parameterize poles, zeros, DC gain,  $f_{T}$  as well as nodes impedances by means of the g<sub>m</sub>/I<sub>d</sub> of transistors. Thanks to this, we can predict amplifier parameters, like the phase margin or the unity-gain frequency, before simulations. With a very simple high-frequency model, it is already possible to reach some of the target specifications. This method can be generalized in order to make automated calculations and thus to save time during the design phase. Furthermore, it is possible to improve the results by means of optimization algorithms using the  $g_m/I_d$  of the transistors as free choice parameters.

References:

[1] Jespers, P. (2009). The gm/ID Methodology, a sizing tool for low-voltage analog CMOS Circuits: The semi-empirical and compact model approaches(Vol. 29). Springer. [2] Razavi, B. (2001). Design of Analog CMOS Integrated Circuits, McGraw-Hill,

#### Université de Mons F.P.Ms - Service d'Electronique et de Microélectronique (SEMi)